Quantum computers are in theory capable of simulating the interactions of molecules at a level of detail far beyond the capabilities of even the largest supercomputers today. Such simulations could revolutionize chemistry, biology and materials science, but the development of quantum computers has been limited by the ability to increase the number of quantum bits, or qubits, that encode, store and access large amounts of data.

In a paper published in the Journal of Applied Physics, a team of researchers at the Georgia Tech Research Institute (GTRI) and Honeywell International have demonstrated a new device that allows more electrodes to be placed on a chip – an important step that could help increase qubit densities and bring us one step closer to a quantum computer that can simulate molecules or perform other algorithms of interest.

"To write down the quantum state of a system of just 300 qubits, you would need 2^300 numbers, roughly the number of protons in the known universe, so no amount of Moore's Law scaling will ever make it possible for a classical computer to process that many numbers," said Nicholas Guise, a GTRI research scientist who led the research. "This is why it's impossible to fully simulate even a modest sized quantum system, let alone something like chemistry of complex molecules, unless we can build a quantum computer to do it."

While existing computers use classical bits of information, quantum computers use "quantum bits" or qubits to store information. Classical bits use either a 0 or 1, but a qubit, exploiting a weird quantum property called superposition, can actually be in both 0 and 1 simultaneously, allowing much more information to be encoded. Since qubits can be correlated with each other in a way that classical bits cannot, they allow a new sort of massively parallel computation, but only if many qubits at a time can be produced and controlled. The challenge that the field has faced is scaling this technology up, much like moving from the first transistors to the first computers.

One leading qubit candidate is individual ions trapped inside a vacuum chamber and manipulated with lasers. The scalability of current trap architectures is limited since the connections for the electrodes needed to generate the trapping fields come at the edge of the chip, and their number are therefore limited by the chip perimeter.

The GTRI/Honeywell approach uses new microfabrication techniques that allow more electrodes to fit onto the chip while preserving the laser access needed.

The team's design borrows ideas from a type of packaging called a ball grid array (BGA) that is used to mount integrated circuits. The ball grid array's key feature is that it can bring electrical signals directly from the backside of the mount to the surface, thus increasing the potential density of electrical connections.

The researchers also freed up more chip space by replacing area-intensive surface or edge capacitors with trench capacitors and strategically moving wire connections.

The space-saving moves allowed tight focusing of an addressing laser beam for fast operations on single qubits. Despite early difficulties bonding the chips, a solution was developed in collaboration with Honeywell, and the device was trapping ions from the very first day.

The team was excited with the results. "Ions are very sensitive to stray electric fields and other noise sources, and a few microns of the wrong material in the wrong place can ruin a trap. But when we ran the BGA trap through a series of benchmarking tests we were pleasantly surprised that it performed at least as well as all our previous traps," Guise said.

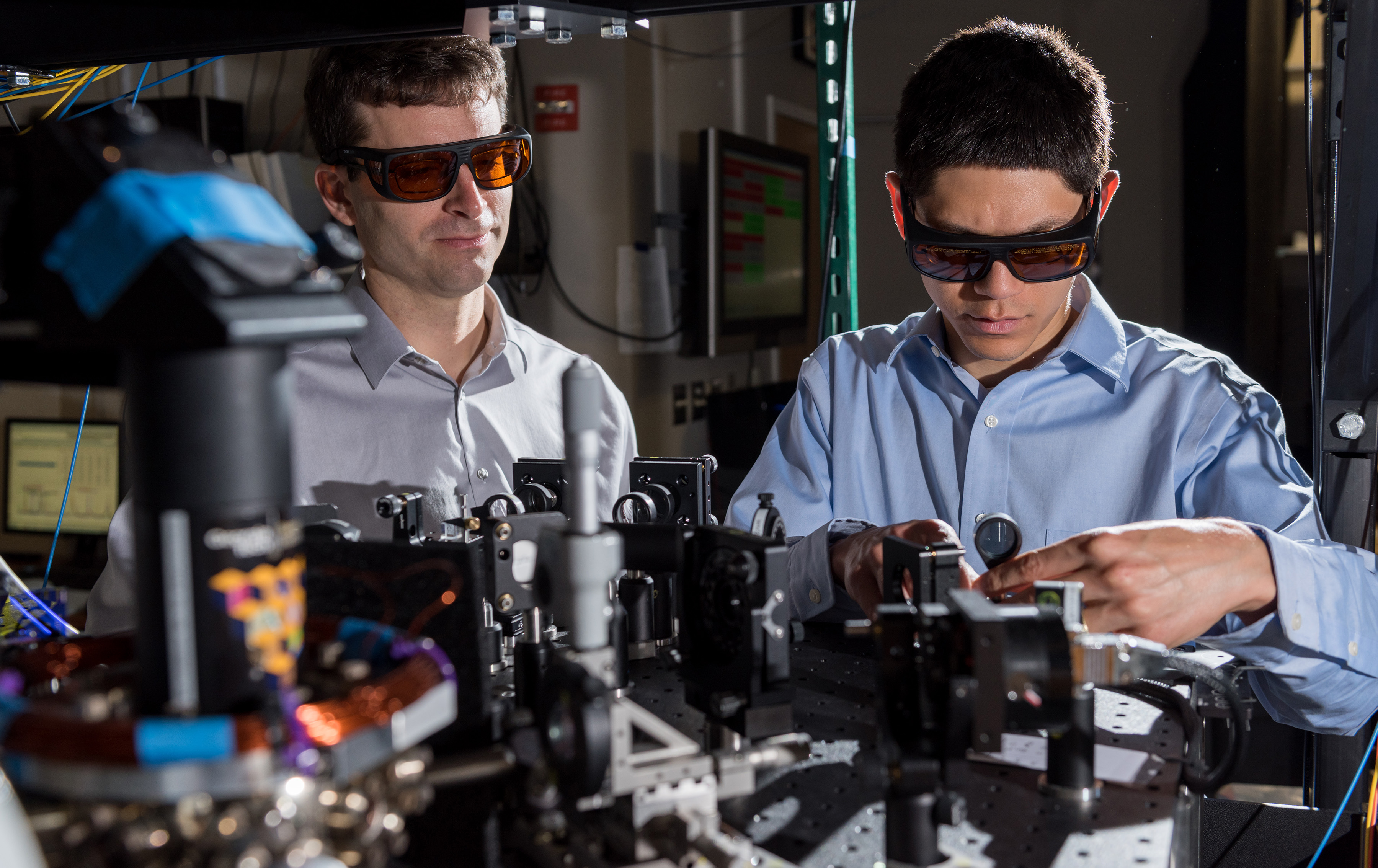

Working with trapped ion qubits currently requires a room full of bulky equipment and several graduate students to make it all run properly, so the researchers say much work remains to be done to shrink the technology. The BGA project demonstrated that it's possible to fit more and more electrodes on a surface trap chip while wiring them from the back of the chip in a compact and extensible way. However, there are a host of engineering challenges that still need to be addressed to turn this into a miniaturized, robust and nicely packaged system that would enable quantum computing, the researchers say.

In the meantime, these advances have applications beyond quantum computing. "We all hope that someday quantum computers will fulfill their vast promise, and this research gets us one step closer to that," Guise said. "But another reason that we work on such difficult problems is that it forces us to come up with solutions that may be useful elsewhere. For example, microfabrication techniques like those demonstrated here for ion traps are also very relevant for making miniature atomic devices like sensors, magnetometers and chip-scale atomic clocks."

This work was funded by the Intelligence Advanced Research Projects Activity (IARPA).

The article, "Ball-grid array architecture for microfabricated ion traps," is authored by Nicholas D. Guise, Spencer D. Fallek, Kelly E. Stevens, K. R. Brown, Curtis Volin, Alexa W. Harter, Jason M. Amini, Robert E. Higashi, Son Thai Lu, Helen M. Chanhvongsak, Thi A. Nguyen, Matthew S. Marcus, Thomas R. Ohnstein and Daniel W. Youngner. It appears in the Journal of Applied Physics and can be accessed at: http://scitation.aip.org/content/aip/journal/jap/117/17/10.1063/1.4917385